Projects

Embedded Systems and Firmware

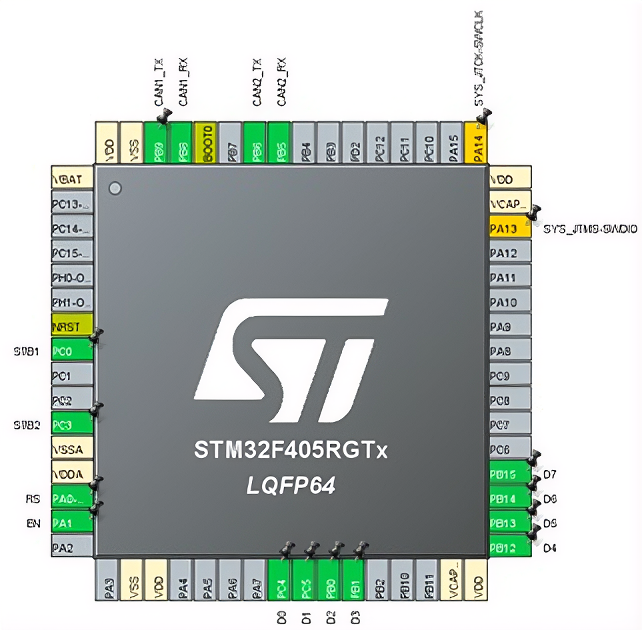

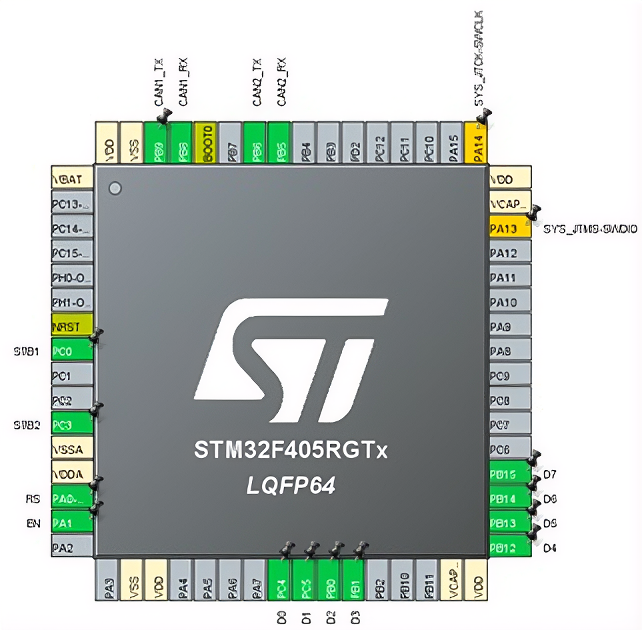

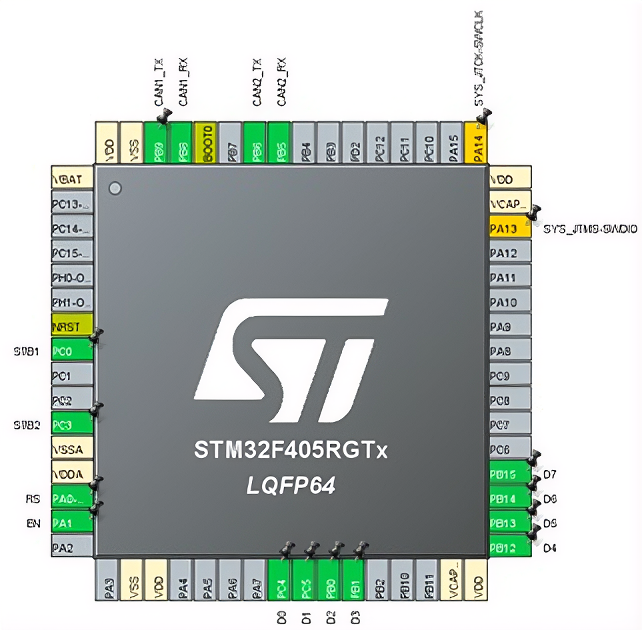

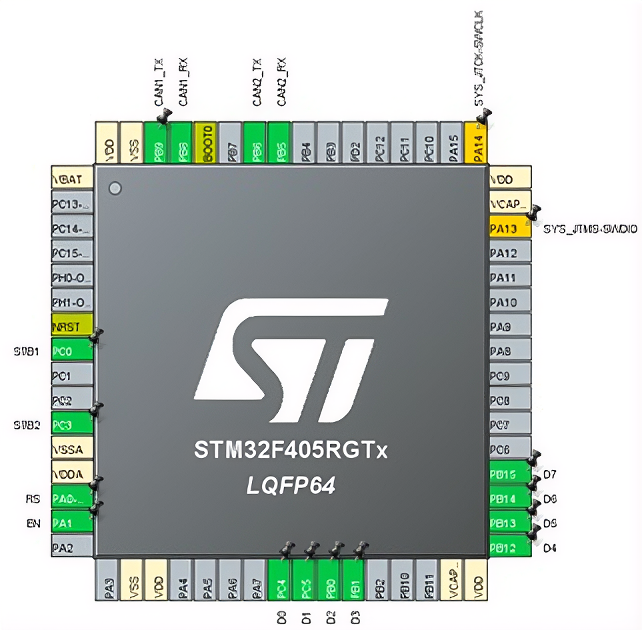

STM32 CAN Communication & Debug Framework

Tech Stack: STM32 •Embedded C •HAL APIs •CAN Protocol •Interrupts •Debugging

Designed an interrupt-driven architecture using filters, FIFOs, mailboxes and timers

to handle asynchronous message traffic under varying system loads. During testing, encountered real issues like message loss, timing mismatches and unstable reception

Debugged these at the register and configuration level, refining the system through iterative validation. Final outcome: Achieved 100% stable communication, supporting 50+ integration and validation cycles, mirroring real automotive testing workflows.

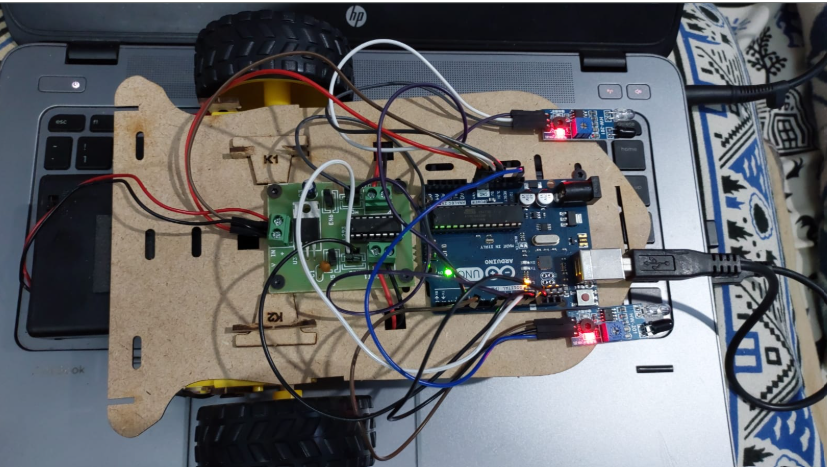

Human Following Robot

Tech Stack: Arduino •Embedded C •IR Sensors •Motor Control •Control Logic •Robotics

Built an autonomous robot that can detect and follow a human in real time using infrared sensing.

Instead of using cameras, designed a lightweight tracking system with dual IR sensors to estimate relative position and continuously adjust movement.

Programmed control logic to handle 10+ real-world behaviors:

→ move forward when aligned

→ turn when the target shifts

→ stop when the signal is lost

During testing, faced challenges like false detections and misalignment, and refined the logic to make the robot respond more smoothly and reliably across different scenarios.

The result: a compact system that demonstrates real-time sensing → decision → actuation loop, forming a foundation for autonomous navigation systems.

Hardware / ASIC / FPGA

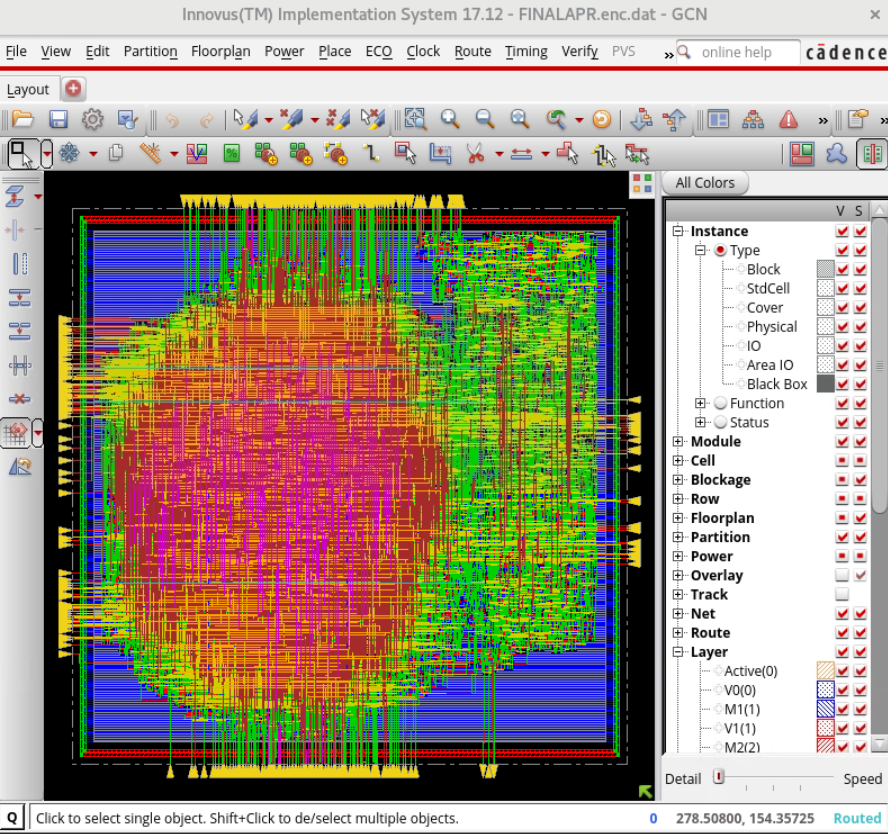

GCN Hardware Accelerator

Tech Stack: SystemVerilog •ASIC Flow •Synopsys Design Compiler •Cadence Innovus •ModelSim •ASAP7 (7nm)

Built a hardware accelerator for Graph Convolutional Networks (GCNs) to explore efficient graph inference at the ASIC level. Designed and integrated RTL modules including:

→ FSM for control flow

→ MAC units for matrix operations

→ Scratchpad memory for intermediate storage

Implemented the full ASIC flow using SystemVerilog + ASAP7 (7nm PDK):

→ RTL design

→ synthesis (Design Compiler)

→ place & route (Innovus)

→ post-synthesis verification

During development, addressed challenges like dataflow coordination, memory access timing, and module integration, refining the architecture through iterative debugging. Final outcome: Achieved 500 MHz post-route frequency and improved verification efficiency by ~40% using automated ModelSim testbenches.

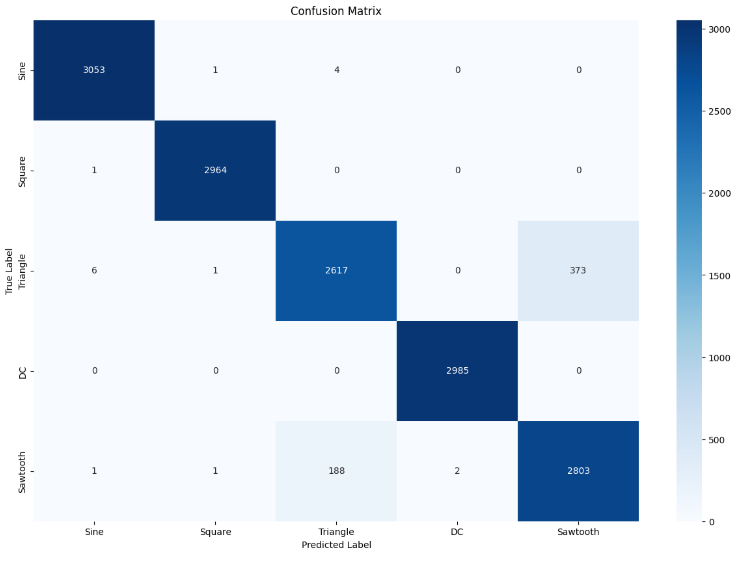

FPGA-Based Signal Implementation

Tech Stack: Verilog/SystemVerilog •FPGA •RTL Design •Simulation •Hardware Validation

Implemented signal processing logic on FPGA to validate real-time data handling in hardware.

Translated algorithmic behavior into hardware-efficient designs, focusing on latency and resource utilization trade-offs.

Verified functionality through simulation

and on-board validation across multiple test cases to ensure correctness under real execution conditions.

Strengthened understanding of how software-level logic maps into timing-constrained hardware systems.

FPGA Processor Communication Project (Ongoing)

Tech Stack: FPGA •Embedded Systems •Digital Communication •Synchronization •System Integration

Building a processor-to-FPGA communication system to enable reliable, low-latency data transfer between compute units. Designing and testing interface mechanisms for:

→ synchronization

→ data exchange

→ control signaling

Currently exploring challenges like timing coordination, protocol design, and system-level integration, with a focus on scalable real-time architectures.

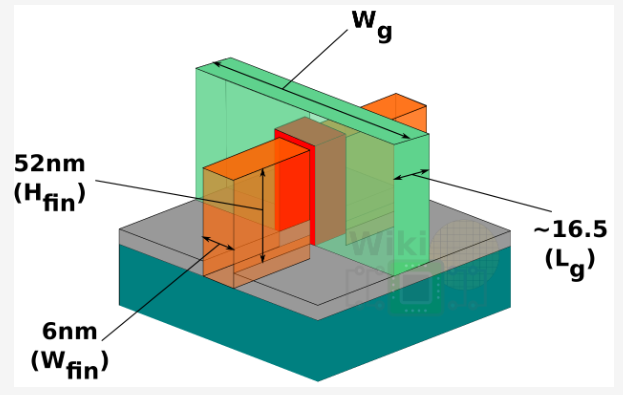

7nm 6T SRAM Design

Tech Stack: Cadence Virtuoso •HSPICE •ASAP7 (7nm) •Transistor-Level Design •Analog Simulation

Designed a 6T SRAM cell in 7nm ASAP7 PDK using Cadence Virtuoso to study memory stability at advanced nodes.

Performed extensive characterization using SPICE simulations:

→ 100+ simulations across operating conditions

→ 20+ transistor sizing configurations

Analyzed key metrics including:

→ static noise margin (SNM)

→ read/write stability

→ performance vs. reliability trade-offs

I Identified optimal sizing strategies to balance stability, power, and performance in scaled technologies.

Machine Learning & Systems

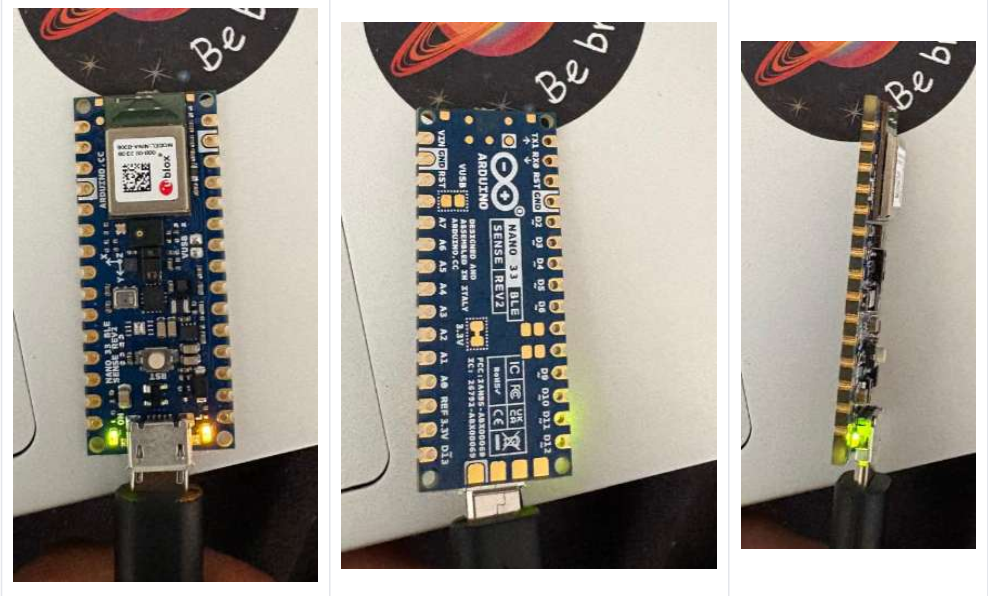

TinyML Keyword Spotting

Tech Stack: Python • TensorFlow/Keras • TinyML • MFCC • Edge AI • Arduino Nano 33 BLE Sense

Built an end-to-end keyword spotting system for real-time audio classification on a microcontroller.

Collected and curated 1300+ labeled audio samples, and extracted MFCC features (40×51) to train a custom CNN (~185K parameters).

Optimized the model for edge deployment by applying INT8 quantization, reducing size to ~21KB while maintaining ~99% test accuracy.

Deployed the model on Arduino Nano 33 BLE Sense, enabling real-time inference under strict memory and compute constraints.

Achieved low-latency on-device inference, demonstrating how ML pipelines can be compressed and deployed efficiently on resource-constrained hardware.

Signal Generation & FFT Visualization Tool

Tech Stack: Python • PyQt • Signal Processing • FFT • Real-Time Systems • Data Visualization

Built a real-time signal processing system to generate, capture, and analyze signals dynamically.

Developed a PyQt-based GUI with integrated FFT module to visualize both time-domain and frequency-domain behavior.

Optimized the sampling pipeline to:

→ reduce latency

→ support higher sampling rates

→ improve real-time responsiveness

During testing, handled challenges like signal noise and sampling inconsistencies, refining the pipeline for stable visualization. Enabled real-time signal diagnostics, bridging software processing with hardware-level signal behavior.

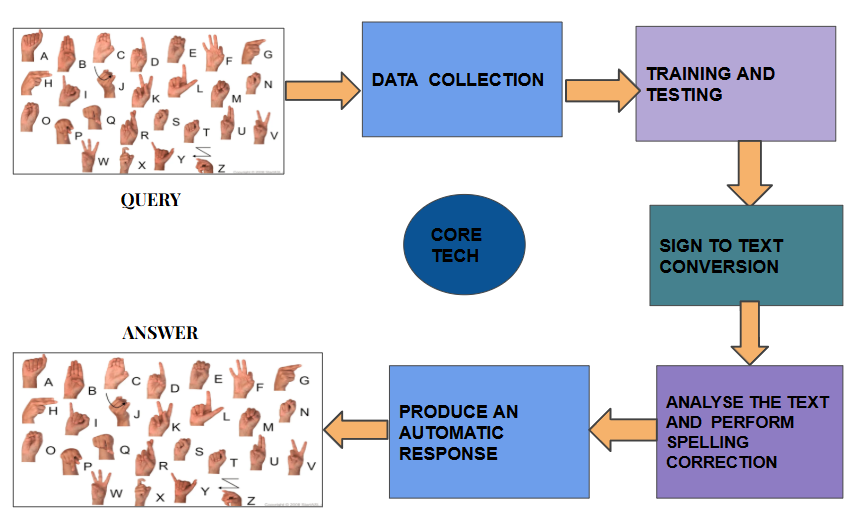

Sign-Kiosk: Real-Time Virtual Assistant (Publication)

Tech Stack: Python •PyQt • Signal Processing •FFT • Real-Time Systems •Data Visualization

Developed a real-time assistive system to recognize sign language gestures and generate contextual responses.

Built the pipeline using:

→ MediaPipe for hand gesture extraction

→ Random Forest for gesture classification

→ RoBERTa for response generation

Achieved ~92% gesture recognition accuracy, enabling reliable interpretation of user input. Designed to improve accessibility by enabling human-computer interaction for individuals with hearing/speech impairments.

Published at ICTCS 2023 (Springer).